ARM Cortex-A53

| Use attributes for filter ! | |

| Cores | 1–4 per cluster |

|---|---|

| L2 cache | 128 KiB – 2 MiB |

| L1 cache | 8–64 KiB |

| Microarchitecture | ARM architecture |

| Successor | ARM Cortex-A55 |

| Designed by | Arm Holdings |

| Core | 1–8 per cluster |

| Fsb speed | 100 MHz to 118 MHz OC |

| Instruct set | ARMv8-A |

| L1 cach | 8–64 KiB |

| L2 cach | 128 KiB – 2 MiB |

| Max cpu clock rate | 400 MHz to 2.30 GHz |

| Successors | ARM Cortex-A55 |

| Date of Reg. | |

| Date of Upd. | |

| ID | 2346568 |

About ARM Cortex-A53

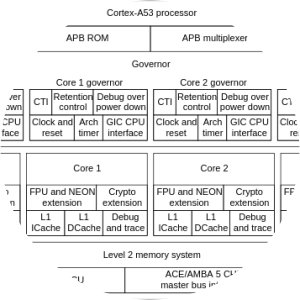

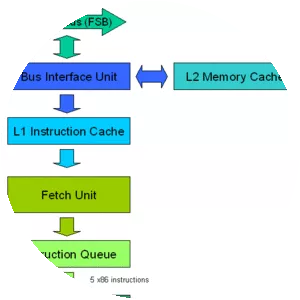

The ARM Cortex-A53 is one of the first two central processing units implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Cambridge design centre, along with the Cortex-A57. The Cortex-A53 is a 2-wide decode superscalar processor, capable of dual-issuing some instructions.